In the evolving landscape of power electronics, Gallium Nitride (GaN) has transitioned from a theoretical “material of the future” to a practical, high-efficiency solution for modern power conversion. For engineers accustomed to Silicon (Si) MOSFETs or IGBTs, adopting GaN is not simply a matter of component swapping. The very characteristics that make GaN superior—specifically its ability to switch at extremely high speeds with minimal reverse recovery charge—introduce a new set of engineering challenges.

The successful implementation of GaN High Electron Mobility Transistors (HEMTs), particularly those utilizing the Gate Injection Transistor (GIT) structure like CoolGaN™, requires a shift in design philosophy. It demands a holistic approach where the device, the gate driver, the printed circuit board (PCB) layout, and thermal management are treated as an inseparable ecosystem.

This article provides a deep technical analysis of the critical design pillars for GaN circuits. We will explore the unique architecture of GIT devices, why current-driven gate methodologies outperform voltage-driven ones, the physics of parasitic inductance in high-speed layouts, and the often-overlooked challenge of measuring Common Mode Transient Immunity (CMTI).

The Five Pillars of GaN Circuit Design

To harness the full potential of wide-bandgap technology, engineers must address five core pillars simultaneously. Neglecting any single pillar can lead to catastrophic failure, electromagnetic interference (EMI) issues, or sub-optimal efficiency that negates the cost premium of using GaN.

- Device Limits: Understanding the absolute maximum ratings, particularly regarding transient voltages and gate constraints.

- Gate Drive Circuit: The interface between control logic and the power switch, responsible for safe and fast switching.

- PCB Layout: The physical arrangement of traces which dictates parasitic inductance and capacitance.

- Commutation Loop: The path of high-frequency current during switching events.

- Thermal Management: Efficiently extracting heat from smaller packages with higher power density.

While thermal management and general device limits are standard concerns in power engineering, the interaction between the Gate Drive and Layout requires specific attention due to the extreme dv/dt and di/dt capabilities of GaN.

For a broader comparison of how these technologies stack up against traditional silicon, you can read our technical analysis on Silicon MOSFET vs. SiC and GaN technologies.

Deconstructing the GaN GIT Structure: A Robust Approach

One of the most robust implementations of e-mode (enhancement mode) GaN is the Gate Injection Transistor (GIT) structure. Unlike standard insulated gate structures found in MOSFETs, the GIT architecture fundamentally alters how the gate interacts with the channel. This difference is crucial for designing reliable drive circuits.

The Gate as a Diode

In a GIT structure, the gate is essentially a p-doped GaN diode. When the device is driven, holes are injected from the gate into the channel, modulating the conductivity of the two-dimensional electron gas (2DEG). This creates a physical behavior where the gate behaves like a diode with a forward voltage drop.

Crucially, this structure provides an intrinsic “self-clamping” mechanism. The forward bias voltage is naturally clamped at approximately 3.5 V to 4 V. Any excess voltage applied to the gate does not stress a fragile oxide layer (as in a MOSFET); instead, it results in increased gate current. This makes the GIT structure exceptionally robust against voltage spikes that would destroy the gate oxide of a traditional silicon device.

Dynamic RDS(on) Stability

A known challenge in early GaN devices was the phenomenon of current collapse or dynamic RDS(on) increase, where the on-resistance would temporarily spike after the device blocked high voltage. This was due to trapped charges in the buffer layers.

The hybrid drain structure used in modern GIT devices (often incorporating p-GaN at the drain side) effectively manages trapped charges. Engineering tests show that for GIT devices, the dynamic resistance increase is typically contained to within 2% of the static value. In contrast, older Schottky gate technologies could see increases as high as 20% to 30%, leading to unpredictable conduction losses and thermal runaway.

The Driving Force: Current vs. Voltage Control

Perhaps the most counter-intuitive aspect of designing for GIT GaN is the shift from “voltage drive” to “current drive.” In standard MOSFET or IGBT driver design, the goal is to apply a specific voltage (e.g., 12V or 15V) to the gate capacitor. However, in the GIT architecture, current drive offers superior reliability and noise immunity.

For those interested in the fundamentals of driving standard power devices, our guide on robust gate drive design provides a solid baseline for comparison.

The Problem with Voltage Drive

Because GaN devices switch at extremely high speeds, the common source inductance (CSI) becomes a significant factor. Even a tiny inductance in the source path generates a voltage ($V = L_{source} \times di/dt$) that opposes the gate drive voltage. Furthermore, the internal gate-to-channel potential is not static; it floats relative to the external source pin depending on the magnitude of the drain current (ID).

Measurements indicate that the internal potential can fluctuate by as much as ±1 V depending on load conditions. If a fixed voltage driver is used, this fluctuation effectively modulates the drive strength, potentially leading to under-driving (higher losses) or over-driving (excessive gate current) during switching transients.

The Solution: Current Source Driving

By treating the gate driver as a current source, engineers can decouple the drive signal from these potential shifts. A constant current source ensures that the requisite number of carriers are injected into the channel regardless of the voltage fluctuations caused by parasitic inductance or ID variation.

Does this require a complex, specialized driver IC? Not necessarily. A “Bulletproof” drive circuit can be implemented using standard off-the-shelf gate drivers intended for MOSFETs or IGBTs, combined with a carefully calculated RC network.

Implementing the RC Network

The RC drive network exploits the diode characteristic of the GIT gate:

- The Capacitor (Con): Provides a high-current impulse during the switching transient to charge the gate capacitance (Ciss) rapidly, ensuring fast turn-on.

- The Resistor (Rss): Sets the steady-state holding current (Iss) once the capacitor is charged. According to Ohm’s Law, the resistor determines the continuous current that keeps the “diode” forward biased and the switch on.

This configuration creates a robust system where the gate voltage naturally clamps itself to the diode’s forward voltage (approx. 3.5V), while the driver output remains high (e.g., 10V or 12V). The voltage difference is dropped across Rss, ensuring a stable, defined current drives the device.

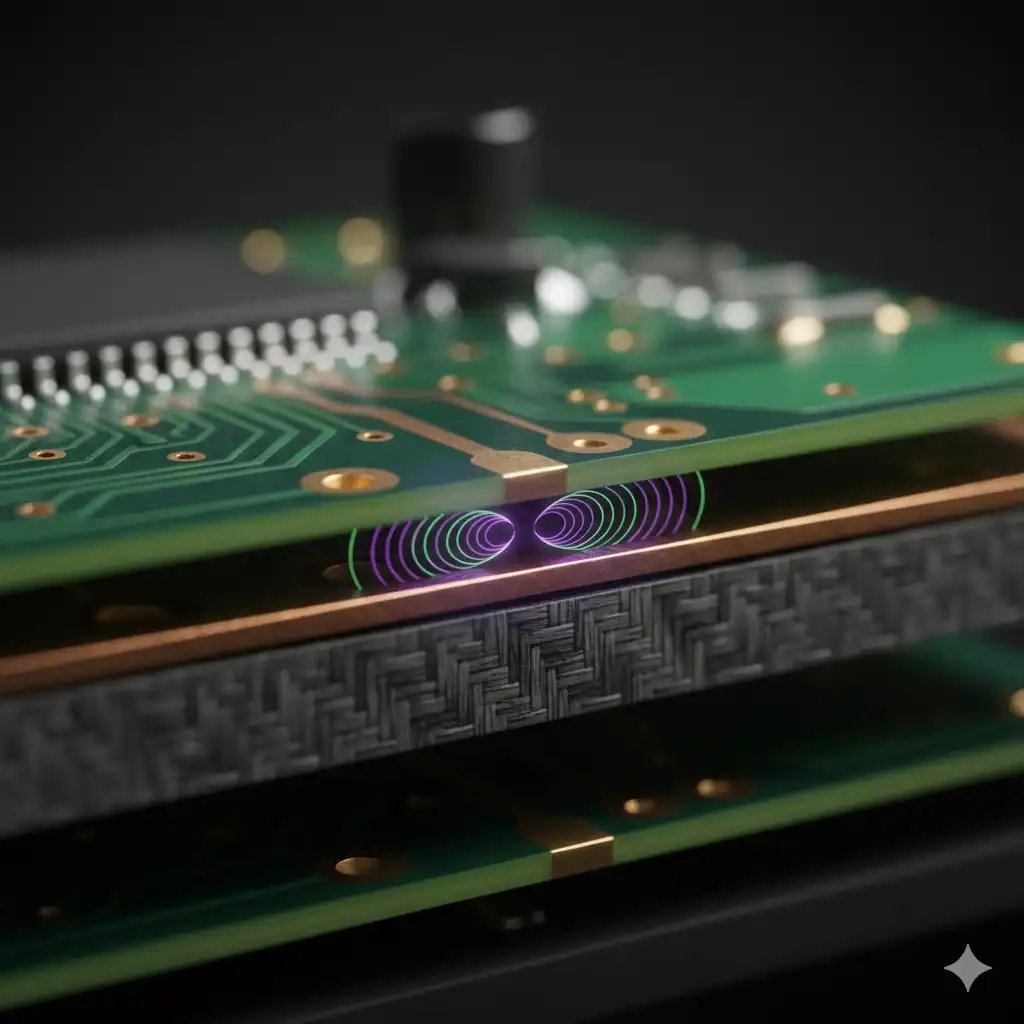

Layout Engineering: Minimizing the Loop

In GaN designs, PCB layout is not merely about connectivity; it is a critical component of the circuit’s electrical parameters. The governing equation for layout success is:

Vovershoot = Lloop × (di/dt)

With GaN devices capable of current slew rates exceeding several amperes per nanosecond (see GaN technology fundamentals), even a parasitic inductance (Lloop) of just 10 nH can result in voltage overshoots of 80 V or more.

This overshoot can exceed device breakdown ratings or cause spurious ringing that triggers false switching.

The “Layer 2” Strategy

To minimize inductance, the total loop area encompassing the gate driver, the gate resistor/capacitor, the GaN device, and the return path must be vanishingly small. The most effective technique is the utilization of vertical flux cancellation.

Engineers should place the gate drive trace on the top layer and a solid ground (return) plane immediately below it on Layer 2. By keeping the dielectric thickness between Layer 1 and Layer 2 extremely thin—ideally around 0.18 mm (approx. 7 mils) or less—the magnetic fields generated by the outgoing and incoming currents cancel each other out effectively. This cancellation significantly reduces the net parasitic inductance.

Furthermore, this Layer 2 copper acts as a Faraday Shield. It prevents the electric field generated by the high-voltage switching node (drain) from coupling noise into the sensitive control circuitry on the layers below. This shielding is vital for maintaining signal integrity in high-density designs.

For related insights on managing inductive loads and ruggedness in power designs, refer to our guide on understanding avalanche energy and ruggedness.

Signal Integrity and Measurement Challenges

Designing the circuit is only half the battle; verifying it is the other. Validating a GaN prototype presents unique instrumentation challenges. The fast switching edges, often ranging from 50 to 100 V/ns, create a severe electromagnetic environment for measurement probes.

The CMTI Conundrum

Common Mode Transient Immunity (CMTI) refers to a system’s ability to reject rapid voltage changes between two isolated grounds. In a half-bridge configuration, the high-side switch floats on the switching node. When the low-side switch turns on or off, the high-side reference ground (the switch node) swings from 0V to 400V (or higher) in mere nanoseconds.

Standard differential voltage probes often lack the CMTI required to measure the high-side gate signal accurately during this transition. A probe with insufficient common-mode rejection will interpret the rapid 400V swing as a differential signal, injecting a “ghost” voltage spike into the measurement. This often leads engineers to believe their circuit has severe ringing or crosstalk, when in reality, the artifact is purely measurement error.

Measurement data suggests that standard high-voltage probes can introduce artificial noise spikes of 6 V or higher when subjected to GaN-speed transients. Given that the threshold voltage of some GaN devices is relatively low, this measurement error makes it impossible to verify safe operation margins reliably.

Best Practices for Validation

To accurately capture the behavior of GaN circuits, the following equipment and techniques are recommended:

- Bandwidth: Oscilloscopes and probes should have a system bandwidth of at least 500 MHz to 1 GHz to capture the true rise and fall times.

- Iso-mode / Optical Isolation: Use optically isolated probes (IsoVu) which provide galvanic isolation close to the tip. These probes offer significantly higher CMTI across the entire frequency spectrum, eliminating common-mode errors.

- Tight Probing points: Avoid long ground leads on probes. Use MMCX connectors or solder-in probe tips directly at the device pins to minimize the pickup loop area.

Conclusion

Designing with GaN, particularly using robust GIT structures like CoolGaN™, unlocks a new tier of efficiency and power density for industrial, automotive, and consumer electronics. However, this performance comes with the requirement for rigorous engineering discipline.

The “drop-in replacement” mentality must be discarded in favor of a systems-level approach. By adopting current-source gate driving to handle potential shifts, utilizing Layer-2 return paths to crush parasitic inductance, and employing high-CMTI instrumentation for validation, engineers can confidently harness the speed of GaN.

As power electronics continue to evolve toward higher frequencies and temperatures (a topic we explore in our article on electronics in extreme environments), mastering these fundamental design principles will be the differentiator between a working prototype and a reliable, mass-production product.